메모리에서 새로운 블럭을 가져와야 하는데,

캐시 테이블에 다른 블럭들로 차있으면, 교체를 해야 한다.

또, 캐시 블록과 메모리의 일관성을 유지하기 위한 대책도 필요하다.

1. 블록 교체 방식

1. 최소 최근 사용(LRU) 구현 비용이 높지만, 최고의 적중률을 보인다.

2. 무작위 방식 : 임의의 캐시 블록을 교체한다. 효율성은 보장하지 못하지만, 구현이 쉽다.

3. 선입 선출 : 먼저 적재된 블록을 먼저 축출한다. 상황에 따라서 무작위보다 안 좋다.

2. 블록 갱신 방식

1. 즉시 쓰기(write-through)

캐시 블록에 쓰기 연시, 메모리에도 수정 내용을 전달한다.

메모리 접근은 비용이 많이 들어서

꼭 필요한 블록에만 이 방식을 적용한다.

2. 나중 쓰기(write-back)

캐시 블록이 수정되면 갱신 비트(dirty bit) 가 수정되는데,

해당 블록이 교체될 때, 이 비트를 보고 갱신된 비트라면,

메모리에 수정된 값을 적용한다.

3. 캐시 실패

1. 강제 실패 (compulsory miss)

메모리 블록의 최초 접근시에 발생하는 실패.

cold miss라고도 한다.

블록의 크기를 늘리거나, 선인출 정책으로 강제 실패를 줄일 수 있다.

2. 용량 실패 (capacity miss)

캐시 메모리의 유한항 용량으로 발생하는 실패.

블록이 교체된 후, 나중에 그 블록을 가져올 때 발생한다.

블록의 크기완 무관하고, 캐시 용량이 프로그램 보다 작으면 반드시 발생한다.

3. 충돌 실패 (collision miss)

집합 연관 사상이나, 직접 사상의 경우

다수의 블록이 동일한 집합이나 블록에 사상되면서 생기는 실패.

완전 연관 사상에서는 이 실패가 발생하지 않는다.

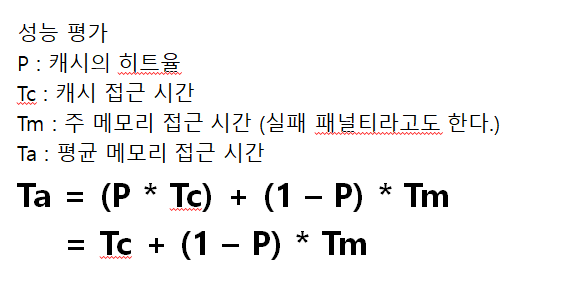

4. 유효 접근 시간

일반적으로, 높은 적중률은 캐시 메모리의 성능이 좋다는 의미지만,

캐시 메모리 성능을 나타낼 땐, 적중률보단 유효 접근 시간을 주로 사용한다.

유효 접근 시간이 작을 수록 좋다.

적중률이 1에 가까우면 Ta 와 Tc는 비슷한 값으로, 속도가 매우 빠르다.

Tm 은 종종 (캐시 접근 시간 + 실패 패널티)로 계산되기도 한다.

Tm 은 메인메모리 접근 시간과, 블록 전송 시간의 합이다.

5. 캐시 메모리 성능 개선

캐시 메모리 성능 개선엔 여러 방법이 있지만,

각 방법에는 그만큼의 패널티가 있다.

| 설계 요인 | 크게 할 경우 | 작게 할 경우 |

| 블록크기 | 적중률 상승 실패 패널티 증가 태그 메모리 부담 감소 |

적중률 감소 실패 패널티 감소 태그 메모리 부담 상승 |

| 캐시 용량 | 하드웨어 부담 상승 적중 시간 증가 |

하드웨어 부담 감소 용량 실패, 충돌 실패 증가 |

| 캐시 연관도 | 정중률 상승 적중 시간 증가 |

적중률 감소 적중 시간 감소 |

참 골때린다. 하나하나 보자.

1. 블록 크기

블록 크기를 증가하면, 공간적 지역성을 더 확보할 수 있어, 적중률이 높아진다.

또한, 블록이 크니, 태그 비트를 적게 사용한다.

하지만, 태그비트가 줄어든 만큼, 블록 비트가 증가해,

블록간 이동시, 비용이 커진다.

2. 캐시 용량

캐시 용량이 작으면, 캐시 미스가 자주 발생한다.

하지만 그렇다고 캐시를 크게 해버리면,

주 메모리가 하나 더 생긴거나 다름 없기 때문에

용량을 무작정 키우는 건 도움이 되지 않는다.

3. 캐시 연관도

캐시 연관도가 증가하면 높아지긴 한다.

특히, 완전 연관 사상에서 효과가 좋다.

하지만 연관도가 커지면, 캐시 탐색시간이 길어지는 문제가 생긴다.

또한, 더 많은 비교기가 필요해지므로, 비용도 많이 든다.

즉, 용량이 적으면 캐시 연관도를 낮춰야 하고,

반대로 용량이 크면 캐시 연관도를 크게 하는게 좋다.

대부분의 컴퓨터는 캐시 메모리가 cpu에 가까울수록 높은 연관도를 사용한다.

즉 cpu - L1 cache - L2 cache - L3 cache - 메모리 구조라면

L3는 캐시 연관도가 작고, L1은 캐시 연관도가 높다.

출처 : 컴퓨터 아키텍처 컴퓨터 구조 및 동작 원리 (한빛 아카데미)

'학교 > 컴퓨터 구조' 카테고리의 다른 글

| 2. 컴퓨터의 성능 (3/3) CPU 성능에 영향을 주는 요소 (0) | 2020.11.28 |

|---|---|

| 2. 컴퓨터의 성능 (2/3) CPU 성능 분석 (0) | 2020.11.28 |

| 2. 컴퓨터의 성능 (1/3) 암달의 법칙 (0) | 2020.11.27 |

| 11. 캐시 메모리 (2/4) 사상(mapping) (0) | 2020.11.26 |

| 11. 캐시 메모리 (1/4) 개요 (0) | 2020.11.26 |